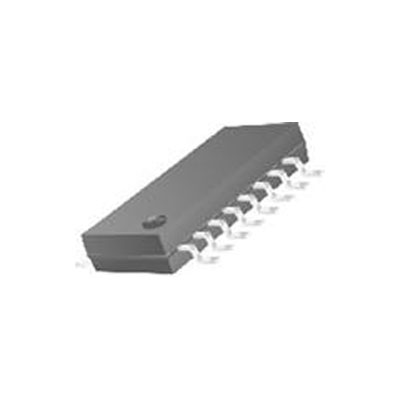

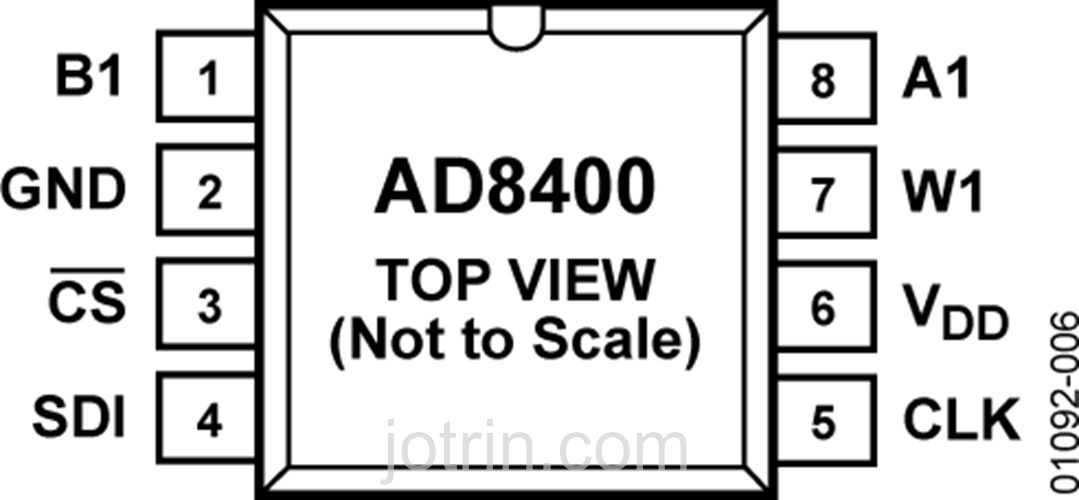

AD8400-A1 Product Details

Each VR has its own VR latch that holds its programmed resistance value. These VR latches are updated from an SPI compatible serial-to-parallel shift register that is loaded from a standard 3-wire serial-input digital interface. Ten data bits make up the data word clocked into the serial input register. The data word is decoded where the first two bits determine the address of the VR latch to be loaded, the last eight bits are data. A serial data output pin at the opposite end of the serial register allows simple daisy-chaining in multiple VR applications without additional external decoding logic.

Feature

- 256-Position

- Replaces 1,2 or 4 Potentiometers

- 1 kΩ, 10 kΩ, 50 kΩ, 100 kΩ

- Power Shutdown - Less than 5 µA

- 3-Wire SPI-Compatible Serial

- Data Input

- 10 MHz Update Data Loading Rate

- 2.7 V to 5.5 V Single-Supply Operation

- Midscale Preset

(Picture: Pinout)